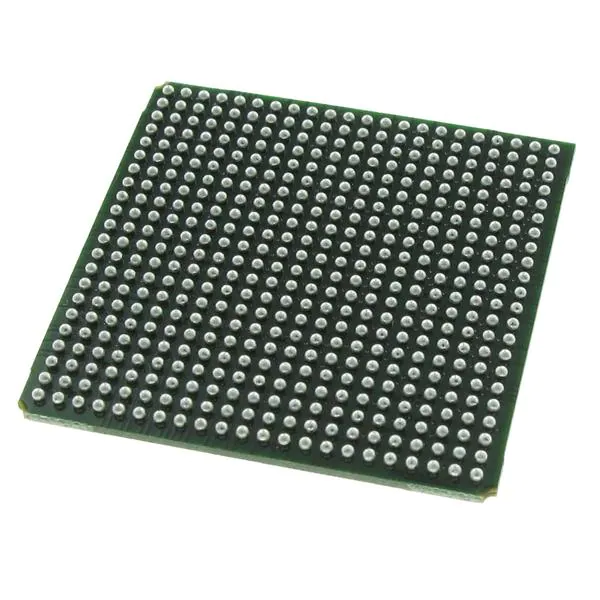

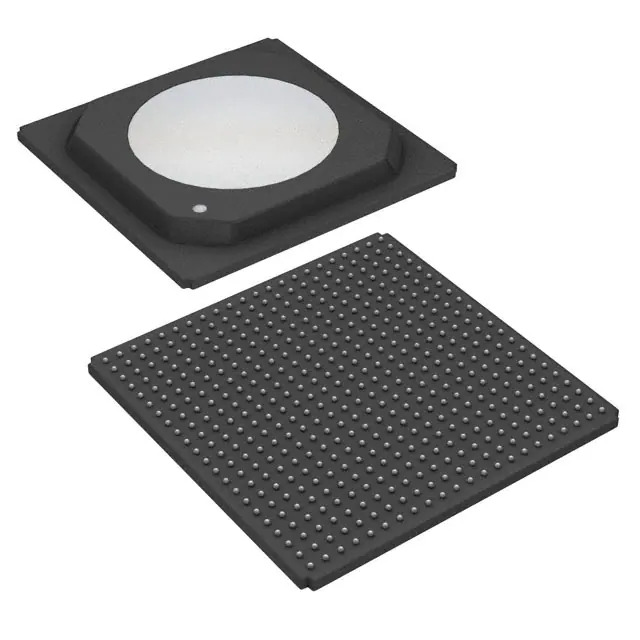

DS34T108GN+

₹9,792.00

Features of DS34T108GN+

- Fully Equipped IC includes 10/100 MAC, TDMoP Engine, and E1/T1 LIUs and Framers.

- Transport of STS-1 TDM or Other CBR Signals Over Packet Networks or E1, T1, E3, or T3

- SAToP, CESoPSN, TDMoIP AAL1, HDLC, Unstructured, Structured, and Structured with CAS Mapping Methods; Adaptive Clock Recovery, Common Clock, External Clock, and Loopback Timing Modes; and Full Support for These Mapping Methods.

- One-per-port, independently programmable On-Chip TDM Clock Recovery Machines.

- Network PDV, Packet Loss, Constant Delay Changes, Frequency Changes, and Other Impairments are Handled by the Clock Recovery Algorithm.

- 64 Independent Bundles/Connections

- Supports IPv4, IPv6, UDP, RTP, L2TPv3, MPLS, and Metro Ethernet Multiprotocol Encapsulation

- Support for VLAN in accordance with 802.1p and 802.1Q Support for MII/RMII/SSMII in the 10/100 Ethernet MAC

Application? of DS34T108GN+

- Extension of TDM Circuit Over PSN:

- PSN Leased-Line Services

- GPON/EPON Over TDM

- Over Cable TDM

- Over Wireless TDM

- Backhaul Over PSN for Cellular

- Multiple Services through a Single PSN

- Transporting HDLC-Based Traffic Over PSN

2490 in stock

Description of DS34T108GN+

Up to eight E1, T1, or serial streams or one high-speed E3, T3, STS-1 or serial stream may be transparently transmitted over IP, MPLS, or Ethernet networks using these IETF PWE3 SAToP/CESoPSN/TDMoIP/HDLC compliant devices. Recovered clocks’ jitter and wander adhere to G.823/G.824, G.8261, and TDM requirements.

Up to 64 independently customizable bundles can carry TDM data. Except for AAL2, all standards-based TDM-over-packet mapping techniques are supported. Additionally supported are frame-based serial HDLC data transfers. has fully functional E1/T1 frames and LIUs built in.

These ICs preserve the ability to use TDM streams at crucial intermediary points while encapsulating the TDM-over-packet solution from analogue E1/T1 signal to Ethernet MII. The DS34T10x devices’ high level of integration reduces cost, board space, and time to market.

MAECENAS IACULIS

Vestibulum curae torquent diam diam commodo parturient penatibus nunc dui adipiscing convallis bulum parturient suspendisse parturient a.Parturient in parturient scelerisque nibh lectus quam a natoque adipiscing a vestibulum hendrerit et pharetra fames nunc natoque dui.

ADIPISCING CONVALLIS BULUM

- Vestibulum penatibus nunc dui adipiscing convallis bulum parturient suspendisse.

- Abitur parturient praesent lectus quam a natoque adipiscing a vestibulum hendre.

- Diam parturient dictumst parturient scelerisque nibh lectus.

Scelerisque adipiscing bibendum sem vestibulum et in a a a purus lectus faucibus lobortis tincidunt purus lectus nisl class eros.Condimentum a et ullamcorper dictumst mus et tristique elementum nam inceptos hac parturient scelerisque vestibulum amet elit ut volutpat.

Reviews

There are no reviews yet.