24C32 32K bit

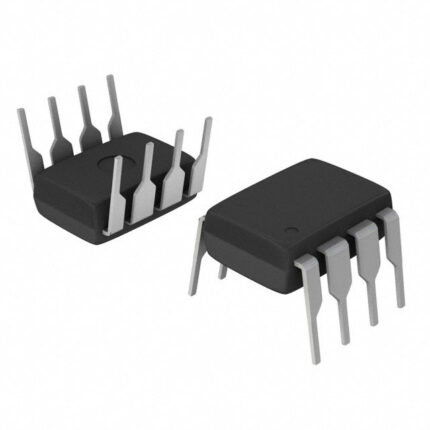

A 4K x 8 (32K bit) Serial Electrically Erasable PROM is the 24C32. This gadget was created for high-end, low-power uses like data collecting or personal communications. The 24C32 has an input cache with a capacity of eight 8-byte pages, or 64 bytes, allowing quick write loads. Additionally, it has a fixed 4K-bit block of ultra-high endurance memory for regularly changing data. Up to the 32K border, the 24C32 may read both randomly and sequentially. Up to eight 24C32 devices can share a bus with functional address lines, providing a maximum address space of 256K bits. This device is perfect for moderate POWER??non-volatile code and data applications thanks to advanced CMOS technology. The typical 8-pin plastic DIP and 8-pin surface mount SOIC packaging for the 24C32 are also available.

Features:-

? Operating voltage range: 4.5V to 5.5V - Maximum read current: 150 A at 5.5V - Peak write current: 3mA at 5.5V - Typical standby current: 1 A

? I2C compliant, industry-standard two-wire bus protocol with 100 kHz and 400 kHz modes

? Autonomous write cycle (including auto-erase)

? Switchable circuitry for data protection

? High Endurance Block has a guaranteed 10,000,000 Erase/Write cycles. - Guaranteed 1,000,000 E/W cycles for Standard Endurance Block

? Available in 8 byte page or byte modes.

? A 64-byte input cache with 1 page by 8 lines for quick write loads.

? Schmitt trigger with filtered inputs to reduce noise

? Ground bounce elimination by output slope control

? A typical write cycle time, byte or page, of 2 ms

? A single bus may support up to 8 chips and 256K bits of total memory.

? Protection from electrostatic discharge > 4000V

? 200-year data retention

? PDIP/SOIC 8-pin packages

? Variable temperatures Industrial (I): -40?C to +85?C Commercial (C): 0?C to +70?C

24LC256-I/SN

Features of? 24LC256-I/SN

? A single supply for use For? 24LC256-I/SN , it drops to 1.7V, whereas 24LC256 devices rise to 2.5V.

? CMOS Low-Power Technology:

Maximum write current is 3 mA. Maximum standby current is 1 A. (I-temp.)

? I2C Compatible, Two-Wire Serial Interface

? Up to eight devices can be cascaded

? Noise-cancelling Schmitt Trigger Inputs

? Ground Bounce is eliminated through output slope control.

? Compatibility with 100 kHz, 400 kHz, and 1 MHz

? Maximum Page Write Time: 5 ms

? Timed Erase/Write Cycle on Your Own

The 64-Byte Page Write Buffer

Equipment Write-Protect

? >4000V ESD Protection

? Over a Million Eraser/Writer Cycles

? >200 years for data retention

Factory programming is accessible for 24LC256-I/SN

24LC256-I/SN is RoHS conformant

24LC512-I/SN

The 24AA512/24LC512/24FC512 (24XX512*) from Microchip Technology Inc. is a 64K x 8 (512 Kbit) Serial Electrically Erasable PROM that can operate over a wide voltage range (1.7V to 5.5V). It was created for cutting-edge, low-power applications including data collection and personal communications. Additionally, this device has a page write capacity of up to 128 bytes of information. Both random and sequential readings up to the 512K barrier are supported by this device. Up to eight devices can share a bus with functional address lines, providing a maximum address space of 4 Mbit. The common 8-pin plastic DIP, SOIJ, SOIC, TSSOP, DFN, and 14-lead TSSOP packaging are also available for this component. The 8-lead Chip Scale package is another option for the 24AA512.

Features:

? A single supply that operates 24AA512 and 24FC512 devices at 1.7V and 24LC512 devices at 2.5V.

? CMOS Low-Power Technology:

- A average active current of 400 uA

- Typical standby current is 100 nA

? Compatible with 2-Wire Serial Interface and I2CTM

? Up to eight devices can be cascaded

? Noise-cancelling Schmitt Trigger Inputs

? Ground Bounce is eliminated through output slope control.

? Compatibility of 100 kHz and 400 kHz clocks

? Maximum Page Write Time 5 ms.

? Timed Erase/Write Cycle on Your Own

? Page Write Buffer of 128 bytes

Equipment Write-Protect

? >4000V ESD Protection

? Over 1,000,000 Erase/Write Cycles

? 200 years of data retention

? The following packages are available: 8-lead PDIP, SOIJ, SOIC, BTSSOP, DFN, Chip Scale, and 14-lead TSSOP.

? RoHS and Pb-Free Compliant

? Ranges of temperatures

Industrial (I): -40?F to 85?F

Vehicle (E): -40 to 125C

25AA320-I/SN

The Microchip Technology Inc. 25AA320/25LC320/25C320 (25XX320*) serial Electrically Erasable PROMs are 32 Kbit. A basic Serial Peripheral Interface (SPI) compliant serial bus is used to access the memory. A clock input (SCK) is required, as well as separate data in (SI) and data out (SO) lines. A Chip Selection (CS) input controls access to the device. The hold pin allows you to suspend communication with the gadget (HOLD). Transitions on the device's inputs will be ignored while it is stopped, excluding Chip Select, enabling the host to service higher priority interrupts.

Features

? CMOS Low-Power Technology:

- Maximum write current: 3 mA

- Typical read current: 500 A

- Typical standby current: 500 nA

? 4096 x 8 Bit Storage

? 32 bytes each page

? Maximum Write Cycle Time: 5 ms

? Erase and write cycles that are self-timed

? Write Block Protection:

- Protect none, 1/4, 1/2, or the entire array.

? Integrated Write Protection:

- Data protection circuitry that is switched on and off

? Latch for write enable

- A write-protection pin

? Read in Sequence

? High dependability:

- Endurance: 1 million E/W cycles

- Data retention: more than 200 years

- ESD protection: more than 4000V

? PDIP, SOIC, and TSSOP packages with 8 pins

? TSSOP Package with 14 Leads

89E516RD2

The SST89E5xxRD2 and SST89V5xxRD2 are FlashFlex51 family 8-bit microcontroller devices designed and manufactured using SST's unique and proprietary Super Flash CMOS semiconductor manufacturing technology. SST's clients gain significantly from the split-gate device structure and thick-oxide tunnelling injector in terms of cost and reliability. The devices are pin-for-pin compatible with ordinary 8051 microcontroller devices and use the 8051 instruction set. The devices include 16/24/40/72 K Byte of on-chip flash EEPROM programme memory that is divided into two separate programme memory blocks. The primary Block 0 has 8/16/32/64K Bytes of internal programme memory space, whereas the secondary Block 1 has 8K Bytes of internal programme memory space.

The 8-KByte secondary block can be identified to the minimum address point in the 8/16/32/64 K Byte address space, as well as concealed from the programme counter and utilised as an independent EEPROM-like data store. In addition to the on-chip EEPROM programme memory of 16/24/40/72 K Bytes, the devices may address up to 64 K Bytes of external programme memory. In addition to 1024 x 8 bits of on-chip RAM, external RAM of up to 64 K Bytes may be addressed.

AT24C512-10PU

The AT24C512 provides 524,288 bits of serial electrically erasable and programmable read only memory (EEPROM) organized as 65,536 words of 8 bits each. The device’s cascadable feature allows up to four devices to share a common two-wire bus. The device is optimized for use in many industrial and commercial applications where lowpower and low-voltage operation are essential. The devices are available in spacesaving 8-pin PDIP, 8-lead EIAJ SOIC, 8-lead JEDEC SOIC, 8-lead TSSOP, 8-lead Leadless Array (LAP), and 8-lead SAP packages. In addition, the entire family is available in 2.7V (2.7V to 5.5V) and 1.8V (1.8V to 3.6V) versions.

AT24C512 Datasheet

AT24C512C-SSHD

The AT24C512C functions as a slave device and communicates with a host controller, also known as the bus master, using a straightforward two-wire digital serial interface that is I2C-compatible. On a serial bus, the master initiates and manages all read and write operations to slave devices, and both the master and slave devices are capable of sending and receiving data. Just two signal lines?Serial Clock (SCL) and Serial Data?make up the serial interface (SDA). The bilateral SDA pin is used to receive command and detailed empirical from the master as well as to transmit data back to the master, while the SCL pin is used to accept the clock signal from the master. To reduce the impact of input spikes and bus noise, the SCL and SDA pins each include Schmitt Triggers and inbuilt spike suppression filters. The Most Significant bit (MSb) is always transmitted first when sending commands or data. After eight bits (one byte) of information have been exchanged during bus communication, the receiving device must answer with an Acknowledge (ACK) or No-Acknowledge (NACK) response bit during such a ninth clock cycle (ack/nack clock cycle) produced by the master. As a result, nine clock cycles are needed to send one byte of data. There must be no gaps or interruptions throughout any data transfer operation since there are no spare clock cycles.

AT24C512C-SSHD Datasheet

AT24CO2

The 1024/2048/4096/8192/16384 bits of serial electrically erasable and programmable read-only memory (EEPROM) provided by the AT24C01A/02/04/08A/16A are structured as 128/256/512/1024/2048 words of 8 bits each. The gadget is designed with a variety of industrial and business applications in mind, where low-power and low-voltage functioning are crucial. The AT24C01A/02/04/08A/16A is accessible through a Two-wire serial interface and is offered in compact 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead MAP, 5-lead SOT23 (AT24C01A/AT24C02/AT24C04), 8-lead TSSOP, and 8-ball dBGA2 packages. There are other variants of the complete series in 2.7V (2.7V to 5.5V) and 1.8V (1.8V to 5.5V) voltage ranges.

Features

Low and Standard Voltage Operation: 2.7 (VCC = 2.7 to 5.5 V) and 1.8 (VCC = 1.8 to 5.5 V)

?128 x 8, 256 x 8, 512 x 8, 1024 x 8, or 2048 x 8 internal organisation (16K)

Bidirectional Data Transfer Protocol, Schmidt Trigger, Filtered Inputs for Noise Suppression, Two-wire Serial Interface, and Compatibility at 100 kHz (1.8V) and 400 kHz (2.7V, 5V)

8-byte page (1K, 2K), 16-byte page, Write Protect Pin for Hardware Data Protection (4K, 8K, 16K) Writing Styles

?High-reliability? Endurance: 1 Million Write Cycles? Data Retention: 100 Years ?Partial Page Writes Allowed ?Self-timed Write Cycle (5 ms max)

?Automotive Grade and Lead-free/Halogen-free Devices Available

?5-lead SOT23,8-lead TSSOP,8-lead PDIP,8-lead JEDEC SOIC,8-lead MAP, and 8-ball dBGA2 Packages

?Die Sales: Bumped Wafers, Waffle Packs, and Wafer Forms

AT24CO4

Features

Low and Standard Voltage Operation: 2.7 (VCC = 2.7 to 5.5 V) and 1.8 (VCC = 1.8 to 5.5 V)

?128 x 8, 256 x 8, 512 x 8, 1024 x 8, or 2048 x 8 internal organisation (16K)

Bidirectional Data Transfer Protocol, Schmidt Trigger, Filtered Inputs for Noise Suppression, Two-wire Serial Interface, and Compatibility at 100 kHz (1.8V) and 400 kHz (2.7V, 5V)

8-byte page (1K, 2K), 16-byte page, Write Protect Pin for Hardware Data Protection (4K, 8K, 16K) Writing Styles

?High-reliability? Endurance: 1 Million Write Cycles? Data Retention: 100 Years ?Partial Page Writes Allowed ?Self-timed Write Cycle (5 ms max)

?Automotive Grade and Lead-free/Halogen-free Devices Available

?5-lead SOT23,8-lead TSSOP,8-lead PDIP,8-lead JEDEC SOIC,8-lead MAP, and 8-ball dBGA2 Packages

?Die Sales: Bumped Wafers, Waffle Packs, and Wafer Forms

The 1024/2048/4096/8192/16384 bits of serial electrically erasable and programmable read-only memory (EEPROM) provided by the AT24C01A/02/04/08A/16A are structured as 128/256/512/1024/2048 words of 8 bits each. The gadget is designed with a variety of industrial and business applications in mind, where low-power and low-voltage functioning are crucial. The AT24C01A/02/04/08A/16A is accessible through a Two-wire serial interface and is offered in compact 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead MAP, 5-lead SOT23 (AT24C01A/AT24C02/AT24C04), 8-lead TSSOP, and 8-ball dBGA2 packages. There are other variants of the complete series in 2.7V (2.7V to 5.5V) and 1.8V (1.8V to 5.5V) voltage ranges.

AT25640B-SSHL-T

The Serial Electrically-Erasable Programmable Read-Only Memory (EEPROM) on the Atmel? AT25320B/640B has 32,768-/65,536-bits and is divided into 4,096/8,192 words with 8 bits each. The device is prepared for usage in a wide range of industrial and commercial settings where moderate and low-voltage functioning are critical requirements. The 8-lead JEDEC SOIC, 8-lead TSSOP, 8-lead UDFN, 8-lead XDFN, and 8-ball VFBGA packages for the AT25320B/640B are available in compact sizes. A 3-wire interface made up of Serial Data Input (SI), Serial Data Output (SO), and Serial Clock is used to access and enable the AT25320B/640B. (SCK). No further erase cycle is necessary before Write since every programming cycle is fully self-timed. Programming one of the four blocks of write security into the status register activates block write protection. For added data security, separate instructions for programme enable and programme disable are given. The WP pin offers hardware data protection to guard against unintentional write attempts to the status register. Any serial communication can be halted using the HOLD pin without having to restart the serial sequence.

AT89C55WD-24PU – Microchip – 8 Bit MCU, 8051

A CMOS 8-bit microcontroller with 20K bytes of Flash programmable read-only memory and 256 bytes of RAM, the AT89C55WD is a low-power, high-performance device. The product is made using high-density flash storage technology from Atmel and has pinout and an instruction set that comply with industry standards 80C51 and 80C52. An ordinary nonvolatile memory programmer can user programme the programme memory thanks to the on-chip Flash. The Atmel AT89C55WD is a potent microcomputer that offers a very flexible and area of business to many embedded control applications by mixing a flexible 8-bit CPU with Flash on a monolithic chip.

The following features are included as standard with the AT89C55WD: A full-duplex serial port, an on-chip oscillator, clock circuitry, three 16-bit timer/counters, 32 I/O lines, 256 bytes of RAM, 20K bytes of Flash, and a six-vector, two-level interrupt architecture. The AT89C55WD also features two software-selectable power-saving modes and static logic allowing operating down to zero frequency. The CPU is turned off in idle mode, but the RAM, timers and counters, serial port, and interruption system are still operational. The oscillator is frozen in the Power-down Mode, which also disables all other chip operations until the next error detection or device reset. However, the RAM contents are saved.

HT9200A

The HT9200A/B tone generators are intended for use with C interfaces. aC can direct them to generate 16 dual tones and 8 single tones using the DTMF pin. The HT9200A has a serial mode, but the HT9200B has a selectable serial/parallel mode interface for a variety of applications such as surveillance systems, building automation, navigation system through telephone lines, communication systems, and so on.