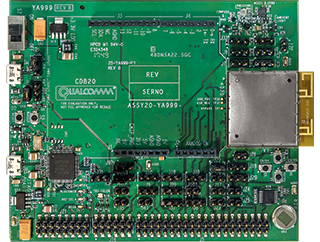

QCA4020-0-217MSP-TR-0D-0

₹677.00

Features of QCA4020

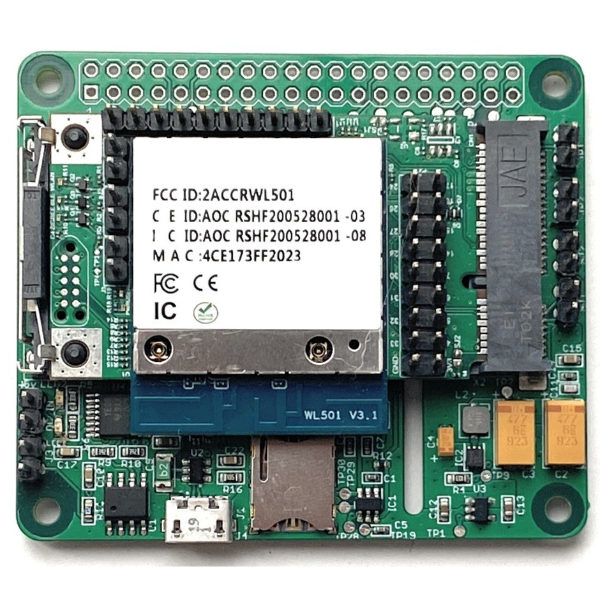

- The QCA4020 tri-mode SoC combines 802.15.4, dual-band Wi-Fi, and Bluetooth 5 technologies.

- Low power, isolated 15.4 SW MAC, 15.4 and BLE drivers, coex management, and Wi-Fi operations processors (QCA4020 only)

- Secure boot, trusted execution environments, encrypted storage, key provisioning, and wireless protocol security are all features of cutting-edge hardware-based security.

- a full range of interfaces and peripherals, including SPI, UART, PWM, I2S, I2C, SDIO, ADC, and GPIOs.

- Low power sensor use cases are made possible by an integrated sensor hub for post-processing.

- Reduced package size enables improved form factors.

Specifications of QCA4020

- Package Type – 11.2 x 11.2mm, 0.65mm pitch, 217-ball BGA (QCA4020)

- Application CPU :

1. Arm Cortex-M4F @ up to 128MHz

2. 32KB- L1 cache controller, XIP from external S-flash

3. Internal Memory: 300+KB RAM reserved for applications - Connectivity/System CPU :

1. Dedicated processor for Bluetooth LE LC and 15.4 MAC

2. Dedicated processor for 802.11 a/b/g/n

3. Isolated Memory: RAM, ROM - Low Power Bluetooth & 15.4 (Separate radios) :

1. Bluetooth v5.0, PA =+4dBm/+10dBm (for Long Range)

2. 802.15.4: 2006 compliant, 15.4e, 2.4GHz DSSS

3. +4dBm/+21dBm (for Long Range) - Wi-Fi (QCA4020 only) : Dual Band, 1×1, HT20, MCS0-7, 2.4/5GHz, PA=+18dBm

- Sensor Hub : Low power HW+App CPU, Interface: I2C, SPI, ADC

- Display : Segmented or character display with SPI or I2C interfaces

- Interfaces :

1. 2C, UART, SPI/Q-SPI, ADC (8ch, 12-bit 1Msps)

2. PWM, SDIO2.0, USB2.0 HS, I2S, GPIOs - Security

1. Secure boot, Secure Storage, HW Crypto Engine

2. HW ECC, 16-bit true random number generator

3. Trusted Execution Environment - Direct Battery Connection : 1.8V-3.6V

Applications

? Internet of Things (IoT)

? Home Automation

? Smart Home

? IoT Hub

? Smart Cities

? Home Entertainment

1841 in stock

Item Description of QCA4020

The QCA4020 SoC is a multi-mode system-on-chip that supports Zigbee, Thread, Bluetooth 5, dual-band Wi-Fi, and 802.15.4-based technologies. In order to support a highly concurrent multiple radio solution, this low power SOC includes a Cortex M4F for application processing, a Cortex M0 for network stack processing, and a separate CPU for Wi-Fi stack.

MAECENAS IACULIS

Vestibulum curae torquent diam diam commodo parturient penatibus nunc dui adipiscing convallis bulum parturient suspendisse parturient a.Parturient in parturient scelerisque nibh lectus quam a natoque adipiscing a vestibulum hendrerit et pharetra fames nunc natoque dui.

ADIPISCING CONVALLIS BULUM

- Vestibulum penatibus nunc dui adipiscing convallis bulum parturient suspendisse.

- Abitur parturient praesent lectus quam a natoque adipiscing a vestibulum hendre.

- Diam parturient dictumst parturient scelerisque nibh lectus.

Scelerisque adipiscing bibendum sem vestibulum et in a a a purus lectus faucibus lobortis tincidunt purus lectus nisl class eros.Condimentum a et ullamcorper dictumst mus et tristique elementum nam inceptos hac parturient scelerisque vestibulum amet elit ut volutpat.

Reviews

There are no reviews yet.